- 全部

- 默认排序

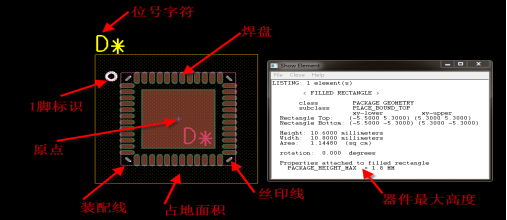

答:一个完整的PCB封装是由许多不同元素组合而成的,不同的器件所需的组成元素也不同。一般来说,封装组成元素包含:沉板开孔尺寸、尺寸标注、倒角尺寸、焊盘、阻焊、孔径、热风焊盘、反焊盘、管脚编号(Pin Number)、管脚间距、管脚跨距、丝印线、装配线、禁止布线区、禁止布孔区、位号字符、装配字符、1脚标识、安装标识、占地面积、器件高度。在Cadence Allegro软件中,以下元素是必须要有的:焊盘(包括阻焊、孔径等内容)、丝印线、装配线、位号字符、1脚标识、安装标识、占地面积、器件最大高度、极

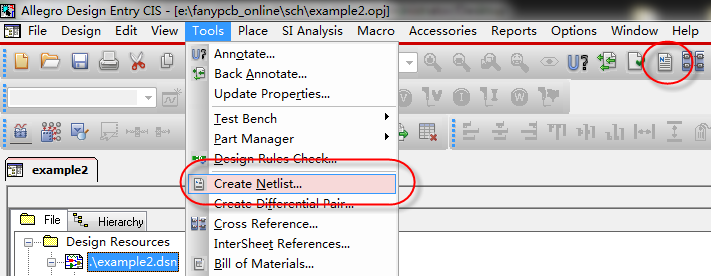

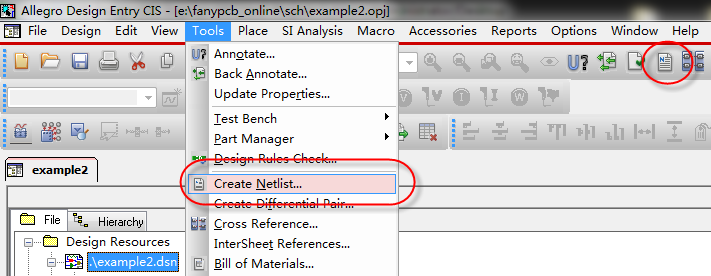

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat Netlist界面中,选择的是PCB Editor,产生Allegro的第一方网表,如图3-69所示; 图3-69 Allegro第一方网表参数设置示意图第三步,输入Allegro第一方网表需要注意下面几个

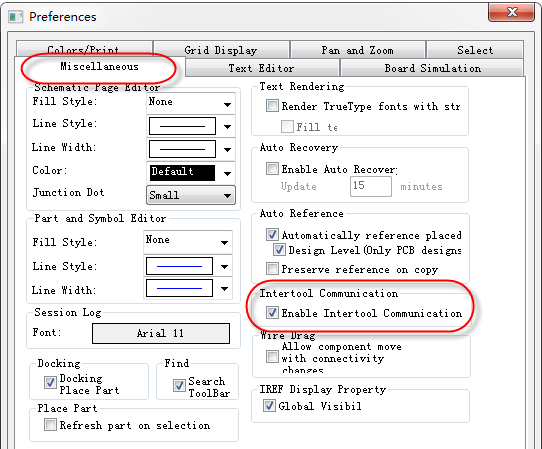

答:orcad与Cadence Allegro的交互式操作需要满足以下两个要求才可以实现:Orcad输出的是Allegro的第一方的网表,Allegro导入的是第一方网表,输出的具体方法见第3.35问;Orcad软件需要勾选以下选项,才可以实现交互式的操作,执行Options→Preference选项,选择Miscellaneous选项,如图3-71所示,在Intertoos Communication选项中,勾上下面的选项,才可以进行交互式操作; 图3-71 交互式操作示

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

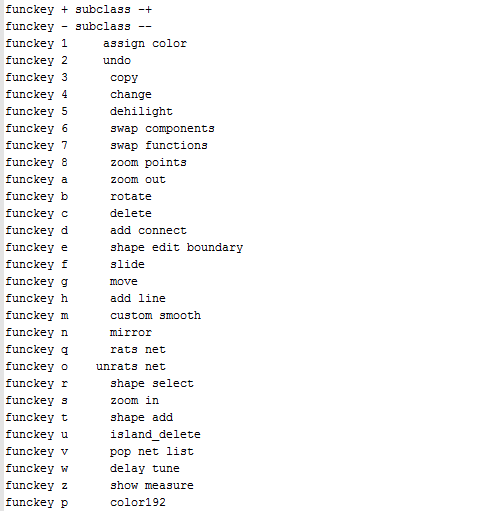

答:我们在使用Allegro软件的时候,绘制PCB文件,在我们使用熟悉之后呢,我们都会增加快捷键的使用,这样可以大大提供我们的效率,我们可以看下,系统默认的快捷键是哪些呢?如图5-1所示

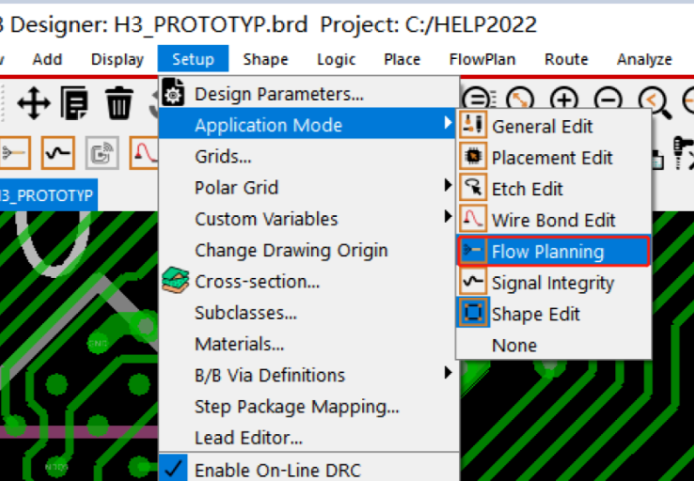

GRE是Global Route Environment的缩写,中文意思为全局布线环境,运用具备阶层化意识的全面绕线引擎与图形式互连流程规划程序。通GRE技术在短时间就可以开发出包含众多互连总线与芯片引脚数的复杂且高速的设计组件。此外,运用

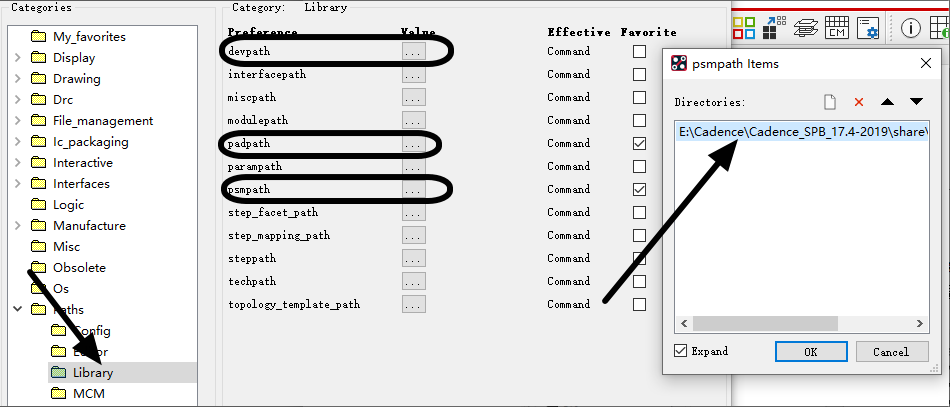

打开Allegro软件,执行菜单命令Setup-User Preferences,在如图所示的用户参数窗口进行库路径的指定,对debpath,padpath及psmpath库进行所需要调用封装库所在路径的指定,这样就可以调用本地的pcb封装

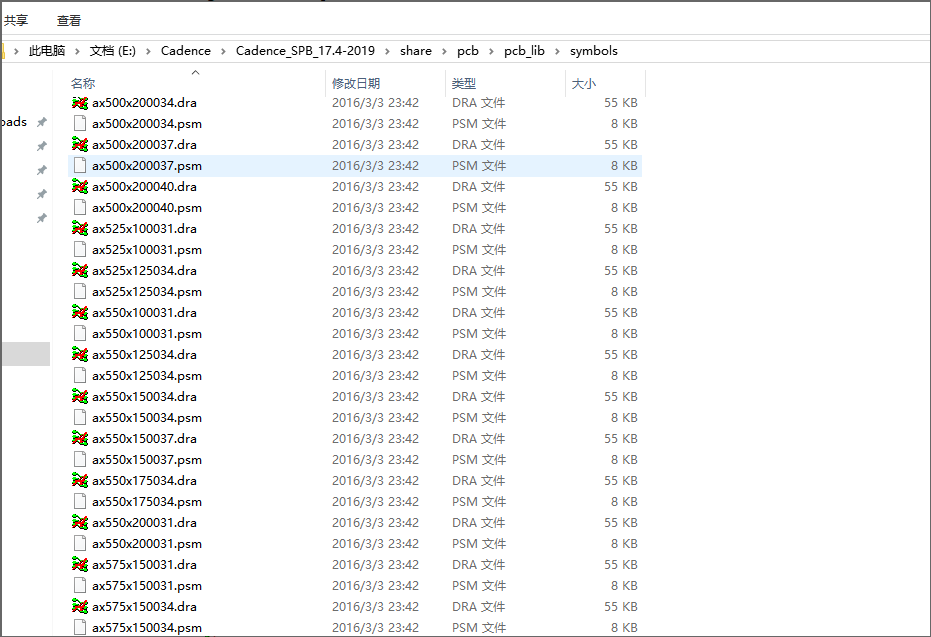

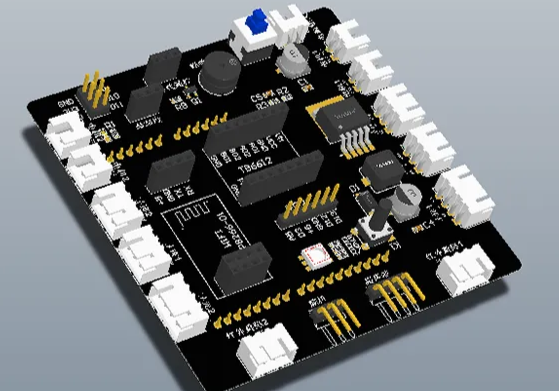

Cadence Allegro软件会自带的一些常用的PCB封装库,大家可以自行调用,它所存储的路径为:X:\Cadence\Cadence_SPB_17.4-2019\share\pcb\pcb_lib\symbols,如图所示:

一个学习信号完整性的layout工程师Cadence Allegro是一款功能比较强大的软件,相比较其他的PCB设计软件来说,界面交互比较友好。其中的快捷键设置就是比较强大,我见过朋友完全使用快捷键进行画图的。但是个人感觉对于新手,还是新熟

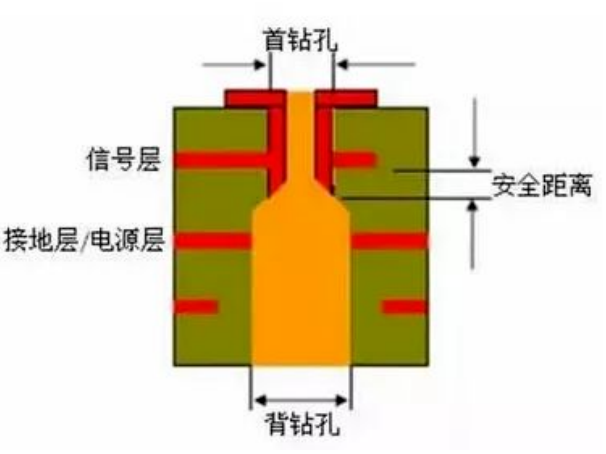

背钻其实就是控深钻比较特殊的一种,在多层板的制作中,例如12层板的制作,我们需要将第1层连到第9层,通常我们钻出通孔(一次钻),然后陈铜。这样第1层直接连到第12层,实际我们只需要第1层连到第9层,第10到第12层由于没有线路相连,像一个柱

扫码关注

扫码关注